#### General Description

The AME8505 series of microprocessor supervisory circuits monitors system voltages from 0.405V to 5V, asserting an open-drain RESET signal when the SENSE voltage drops below a preset threshold or when the manual reset ( $\overline{MR}$ ) pin drops to a logic low. The RESET output remains low for the user-adjustable delay time after the SENSE voltage and  $\overline{MR}$  return above the respective thresholds.

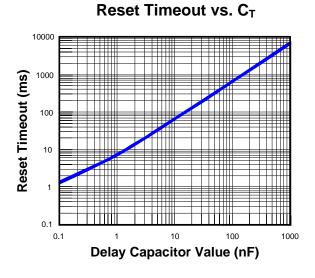

The AME8505 device adopts a precision reference to achieve 0.5% threshold accuracy for  $V_{IT} \leq 3.3V$ . The reset delay time can be set to 20ms by disconnecting the  $C_T$  pin, 300ms by connecting the  $C_T$  pin to  $V_{DD}$  using a resistor or can be user-adjusted between 1.25ms and 10s by connecting the  $C_T$  pin to an external capacitor. The AME8505 device has a very low typical quiescent current of 1.7µA, so it is well-suited to battery-powered applications.

#### Features

- Power-On Reset Generator with Adjustable Delay Time: 1.25ms to 10s

- Very Low Quiescent Current: 1.7µA

- High Threshold Accuracy: 0.5% Typical

- Fixed Threshold Voltages for Standard Voltage from 0.9V to 5V

- Adjustable Voltage Down to 0.405V are Available

- Provide MR Input

- Open-Drain RESET Output

- Temperature Range: -40°C to +125°C

- SOT-26 and DFN-6D(2x2x0.75mm) Packages

#### Application

- DSP or Microcontroller Applications

- Notebook and Desktop Computers

- PDAs and Hand-Held Products

- Portable and Battery-Powered Products

- FPGA and ASIC Applications

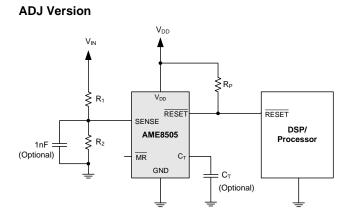

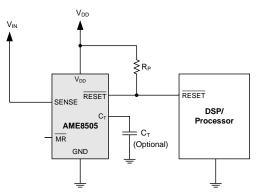

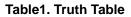

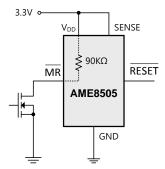

#### Typical Application Schematic

**Fixed Version**

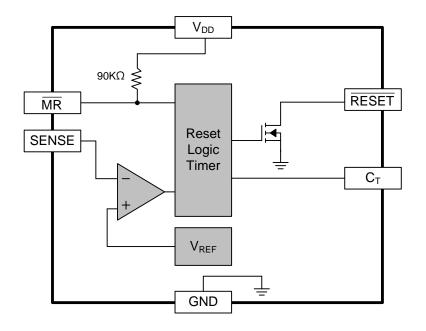

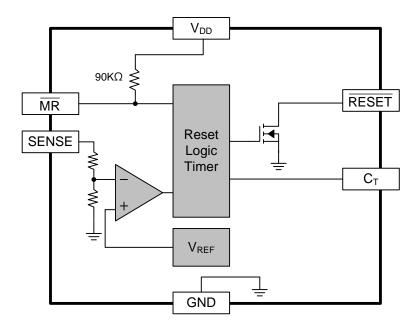

#### Block Diagram

Adjustable Voltage Version

Fixed Voltage Version

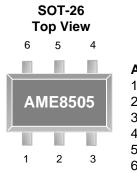

#### ■ Pin Configuration

## AME8505-AEYxxx

| ۱.  | RESET                |

|-----|----------------------|

| 2.  | GND                  |

|     | MR<br>C <sub>T</sub> |

| ••• | 01                   |

- 5. SENSE

- 6.  $V_{DD}$

DFN-6D (2x2x0.75mm) Top View

#### AME8505-AVYxxx

- 1. V<sub>DD</sub> 2. SENSE

- 3. <u>C</u><sub>T</sub>

- 4. MR

- 5. GND

- 6. RESET

## Pin Description

| Pin No. |                        |                 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|------------------------|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOT-26  | DFN-6D<br>(2x2x0.75mm) | Pin Name        | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1       | 6                      | RESET           | 0   | RESET is an open-drain output that is driven to a low-<br>impedance state when RESET is asserted (either the<br>SENSE input is lower than the threshold voltage (V <sub>IT</sub> ) or the<br>MR pin is set to a logic low). RESET will keep low<br>(asserted) for the reset period after both SENSE is above<br>V <sub>IT</sub> and MR is set to a logic high. A pull-up resistor from<br>10kΩ to 1MΩ should be used on this pin, and allows the<br>reset pin to attain voltages higher than V <sub>DD</sub> . |

| 2       | 5                      | GND             | NA  | Ground pin. This pin should be connected to PCB ground reference.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3       | 4                      | MR              | Ι   | Manual Reset Input pin. $\overline{MR}$ low asserts $\overline{RESET}$ .<br>$\overline{MR}$ is internally tied to V <sub>DD</sub> by 90k $\Omega$ a pull-up Resistor.                                                                                                                                                                                                                                                                                                                                          |

| 4       | 3                      | CT              | I   | Reset Period Programming pin. Connecting this pin to $V_{DD}$<br>through a $40k_{\Omega}$ to $200k_{\Omega}$ resistor or leaving it open results<br>in fixed reset delay times. Connecting this pin to a ground<br>referenced capacitor ( $\geq 100pF$ ) gives a user programmable<br>reset delay time.                                                                                                                                                                                                        |

| 5       | 2                      | SENSE           | I   | This pin is connected to the voltage to be monitored. If the voltage at this terminal drops below the threshold voltage $V_{IT}$ , then $\overrightarrow{\text{RESET}}$ is asserted. SENSE does not necessary monitor $V_{DD}$ , it can monitor any voltage lower than $V_{DD}$ .                                                                                                                                                                                                                              |

| 6       | 1                      | V <sub>DD</sub> | Ι   | Supply Voltage. A $0.1_{\mu}F$ ceramic capacitor placed close to this pin is helpful for transient and parasitic.                                                                                                                                                                                                                                                                                                                                                                                              |

| NA      | Pad                    | Thermal<br>Pad  | NA  | Thermal Pad. Connect to ground plane to enhance thermal performance of package.                                                                                                                                                                                                                                                                                                                                                                                                                                |

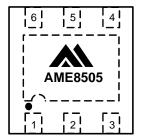

## Ordering Information

| Pin Con  | figuration         | Package Type | Number of Pins | Threshold Voltage |

|----------|--------------------|--------------|----------------|-------------------|

| A        | 1. RESET           | E: SOT-2X    | Y: 6           | ADJ: 0.405V       |

| (SOT-26) | 2. GND             | V: DFN       |                | 084: 0.84V        |

|          | 3. MR              |              |                | 112: 1.12V        |

|          | 4. C <sub>T</sub>  |              |                | 167: 1.67V        |

|          | 5. SENSE           |              |                | 279: 2.79V        |

|          | 6. V <sub>DD</sub> |              |                | 307: 3.07V        |

|          |                    |              |                | 465: 4.65V        |

| A        | 1. V <sub>DD</sub> |              |                |                   |

| (DFN-6D) | 2. SENSE           |              |                |                   |

|          | 3. C <sub>T</sub>  |              |                |                   |

|          | 4. MR              |              |                |                   |

|          | 5. GND             |              |                |                   |

|          | 6. RESET           |              |                |                   |

|          |                    |              |                |                   |

## Absolute Maximum Ratings

| Parameter          | Symbol                                                                    | Value                         | Unit |

|--------------------|---------------------------------------------------------------------------|-------------------------------|------|

|                    | V <sub>DD</sub>                                                           | -0.3 to 7                     |      |

| Voltage            | V <sub>CT</sub>                                                           | -0.3 to V <sub>DD</sub> + 0.3 | V    |

|                    | $V_{\overline{\text{RESET}}}, V_{\overline{\text{MR}}}, V_{\text{SENSE}}$ | -0.3 to 7                     |      |

| Current            | RESET                                                                     | -5 to 5                       | mA   |

|                    | НВМ                                                                       | ±2000                         | V    |

| ESD Classification | MM                                                                        | ±200                          | V    |

|                    | CDM                                                                       | ±1000                         | V    |

## Recommended Operation Conditions

| Parameter                  | Symbol             | Rating               | Unit |

|----------------------------|--------------------|----------------------|------|

| Input Supply Voltage       | V <sub>DD</sub>    | 1.7 to 6.5           |      |

| $C_T$ Pin Voltage          | V <sub>CT</sub>    | 0 to V <sub>DD</sub> |      |

| Sense Pin Voltage          | V <sub>SENSE</sub> | 0 to 6.5             | V    |

| MR Pin Voltage             | V <sub>MR</sub>    | 0 to 6.5             |      |

| RESET Pin Voltage          | V <sub>RESET</sub> | 0 to 6.5             |      |

| RESET Pin Current          | IRESET             | 0.0003 to 5          | mA   |

| Junction Temperature Range | TJ                 | -40 to +125          |      |

| Ambient Temperature Range  | T <sub>A</sub>     | -40 to +85           | °C   |

| Storage Temperature Range  | T <sub>STG</sub>   | -65 to +150          |      |

### Thermal Information

| Parameter                   | Package                               | Die Attach              | Symbol                         | Maximum | Unit    |  |  |

|-----------------------------|---------------------------------------|-------------------------|--------------------------------|---------|---------|--|--|

| Thermal Resistance*         | SOT-26                                | Conductive Energy       | 0                              | 81      | °C (\\) |  |  |

| (Junction to Case)          | DFN-6D                                | Conductive Epoxy        | Conductive Epoxy $\theta_{JC}$ |         | °C / W  |  |  |

| Thermal Resistance          | SOT-26                                | Conductivo Enovy        | 0                              | 260     | °C/W    |  |  |

| (Junction to Ambient)       | DFN-6D                                | Conductive Epoxy        | $\theta_{JA}$                  | 66      | C / W   |  |  |

| Internal Dower Dissipation  | SOT-26                                | Conductive Energy       | P <sub>D</sub>                 | 400     | ~)\/    |  |  |

| Internal Power Dissipation  | DFN-6D                                | DFN-6D Conductive Epoxy |                                | 1515    | mW      |  |  |

| Lead Temperature (soldering | Lead Temperature (soldering 10 sec)** |                         |                                |         |         |  |  |

\* Measure  $\theta_{\text{jc}}$  on top of package.

\*\* MIL-STD-202G 210F

#### Electrical Specifications

$1.7V ~\leq~ V_{DD} ~\leq~ 6.5V, R_{LRESET}$  = 100k $\Omega$ ,  $C_{LRESET}$  = 50pF,  $T_A$  = 25°C, unless otherwise specified

| Param                               | etei            | r                 | Symbol                                                                                               | Test Condition                                                                                | Min           | Тур   | Max             | Units            |

|-------------------------------------|-----------------|-------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------|-------|-----------------|------------------|

| Supply Voltage Range                |                 | V <sub>DD</sub>   |                                                                                                      | 1.7                                                                                           |               | 6.5   | V               |                  |

| Supply Current                      |                 | 1                 | $V_{DD} = 3V$ , $\overline{RESET}$ not asserted<br>$\overline{MR}$ , $\overline{RESET}$ , $C_T$ Open |                                                                                               | 1.4           |       |                 |                  |

|                                     |                 |                   | I <sub>DD</sub>                                                                                      | $V_{DD} = 6.5V, \overline{RESET}$ not asserted<br>$\overline{MR}, \overline{RESET}, C_T Open$ |               | 1.7   |                 | μA               |

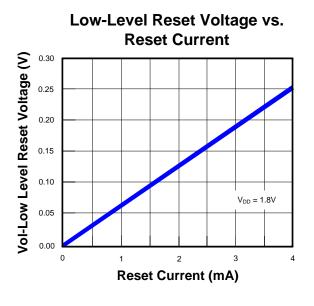

| Low-Level Outp                      | <del>1</del> \/ | oltago            | V <sub>OL</sub>                                                                                      | $1.3V~\leq~V_{DD}~\leq~1.8V\text{, }I_{OL}\text{ = }0.4\text{mA}$                             |               |       | 0.3             | v                |

|                                     | uiv             | onage             | V OL                                                                                                 | 1.8V $\leq$ V_{DD} $\leq$ 6.5V, I_{OL} = 1mA                                                  |               |       | 0.4             | v                |

| Power-Up Outp                       | ut V            | oltage            | $V_{POR}$                                                                                            | $V_{OL(MAX)} = 0.2V, I_{\overline{RESET}} = 15 \mu A$                                         |               |       | 0.8             | V                |

| Negative-going I<br>Accuracy        | npu             | t Threshold       | V <sub>IT</sub>                                                                                      |                                                                                               | -2            |       | 2               | %                |

| Hysteresis On                       | А               | DJ Version        | V                                                                                                    |                                                                                               |               | 1.5   | 3               | 0/ \/            |

| V <sub>IT</sub> PIN                 | F               | ixed Version      | V <sub>HYS</sub>                                                                                     |                                                                                               |               | 1     | 2.5             | %V <sub>IT</sub> |

| MR Internal Pul                     | ll-Up           | Resistance        | $R_{\overline{MR}}$                                                                                  |                                                                                               | 70            | 90    |                 | kΩ               |

| Input Current at                    | AI              | OJ Version        |                                                                                                      | $V_{SENSE} = V_{IT}$                                                                          | -25           |       | 25              | nA               |

| SENSE pin                           | Fi              | xed Version       | I <sub>SENSE</sub>                                                                                   | $V_{SENSE} = 6.5V$                                                                            |               | 1.7   |                 | μA               |

| RESET Leakag                        | ge C            | urrent            | I <sub>OH</sub>                                                                                      | $V_{RESET} = 6.5V, RESET not asserted$                                                        |               |       | 300             | nA               |

| Input Capacitan                     | ice,            | $C_{T}$ pin       | C <sub>IN</sub>                                                                                      | $V_{IN} = 0V$ to $V_{DD}$                                                                     |               | 5     |                 | рF               |

| any pin                             |                 | Other pins        | CIN                                                                                                  | $V_{IN} = 0V$ to 6.5V                                                                         |               | 5     |                 | рі               |

| MR Input Logic                      | : Lov           | N                 | V <sub>IL</sub>                                                                                      |                                                                                               | 0             |       | $0.3^{*}V_{DD}$ | V                |

| MR Input Logic                      | : Hig           | h                 | V <sub>IH</sub>                                                                                      |                                                                                               | $0.7^*V_{DD}$ |       |                 | V                |

| Input Pulse Wid                     | lth             | SENSE             | tu                                                                                                   | $V_{IH} = 1.05 \ V_{IT}, \ V_{IL} = 0.95 \ V_{IT}$                                            |               | 20    |                 | μS               |

| to RESET                            |                 | MR                | t <sub>w</sub>                                                                                       | $V_{IH}=0.7~V_{DD},~V_{IL}=0.3~V_{DD}$                                                        |               | 0.001 |                 | μΟ               |

|                                     | C <sub>T</sub>  | = Open            |                                                                                                      |                                                                                               | 12            | 20    | 28              | mS               |

| RESET Delay                         | C <sub>T</sub>  | = V <sub>DD</sub> | t <sub>d</sub>                                                                                       |                                                                                               | 180           | 300   | 420             | mS               |

| Time                                | C <sub>T</sub>  | = 100pF           | ۰d                                                                                                   |                                                                                               | 0.75          | 1.25  | 1.75            | mS               |

| C <sub>T</sub> = 180nF              |                 |                   |                                                                                                      | 0.7                                                                                           | 1.2           | 1.7   | S               |                  |

| Propagation<br>Delay                |                 |                   | $V_{\text{IH}}=0.7 \; V_{\text{DD}},  V_{\text{IL}}=0.3 \; V_{\text{DD}}$                            |                                                                                               | 150           |       | nS              |                  |

| High to Low<br>Level RESET<br>Delay |                 | ENSE to           |                                                                                                      | $V_{IH} = 1.05 V_{IT}, V_{IL} = 0.95 V_{IT}$                                                  |               | 20    |                 | μS               |

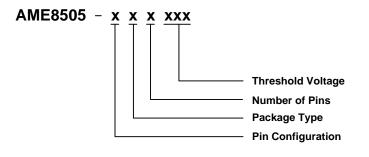

Timing Diagram

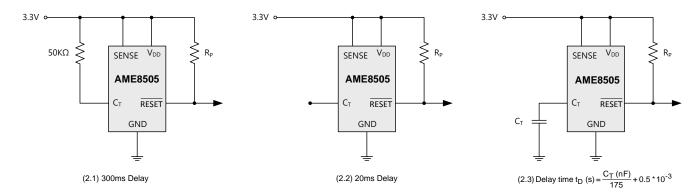

| MR | SENSE > V <sub>IT</sub> | RESET |

|----|-------------------------|-------|

| L  | 0                       | L     |

| L  | 1                       | L     |

| Н  | 0                       | L     |

| Н  | 1                       | н     |

#### Normal Operation (V<sub>DD</sub> > V<sub>DD(min)</sub>)

When  $V_{DD}$  is greater than  $V_{DD(min)}$ , the RESET signal is determined by the voltage on the SENSE pin and the logic state of MR.

$\overline{\text{MR}}$  high: When the voltage on V<sub>DD</sub> is greater than 1.7V for a time of the selected t<sub>D</sub>, the  $\overline{\text{RESET}}$  signal corresponds to the voltage on SENSE relative to V<sub>IT</sub>.

MR low: in this mode, RESET is held low regardless of the value of the SENSE pin.

#### Above Power-On Reset but Less Than $V_{DD(min)}$ ( $V_{POR} < V_{DD} < V_{DD(min)}$ )

When the voltage on  $V_{DD}$  is less than the device  $V_{DD(min)}$  voltage, and greater than the power-on reset voltage ( $V_{POR}$ ), the RESET signal is asserted and low impedance, respectively, regardless of the voltage on the SENSE pin.

#### Below Power-On Reset (V<sub>DD</sub> < V<sub>POR</sub>)

When the voltage on  $V_{DD}$  is lower than the required voltage ( $V_{POR}$ ) needed to internally pull the asserted output to GND,  $\overline{RESET}$  is undefined and should not be relied upon for proper device function.

#### Application Information

The AME8505 device is designed to assert a  $\overrightarrow{RESET}$  signal when either the SENSE pin voltage drops below V<sub>IT</sub> or  $\overrightarrow{MR}$  is driven low. The  $\overrightarrow{RESET}$  output remains asserted for a user-adjustable time after both  $\overrightarrow{MR}$  and SENSE voltages return above their respective thresholds.

#### **Feature Description**

The AME8505 device is designed to assert a  $\overrightarrow{\text{RESET}}$  signal when either the SENSE pin voltage drops below V<sub>IT</sub> or  $\overrightarrow{\text{MR}}$  is driven low. The  $\overrightarrow{\text{RESET}}$  output remains asserted for a user-adjustable time after both  $\overrightarrow{\text{MR}}$  and SENSE voltages return above their respective thresholds. A broad range of voltage threshold and reset delay time options are available for the AME8505 device, allowing these devices to be used in a wide arrange of applications.

The ADJ-version AME8505 can be set to any voltage above 0.405V using an external resistor divider. Two preset delay times are also user-selectable: connecting the  $C_T$  pin to  $V_{DD}$  results in a 300ms reset delay, whereas leaving the  $C_T$  pin open yields a 20ms reset delay. In addition, connecting a capacitor between  $C_T$  and GND allows the designer to select any reset delay period from 1.25ms to 10s.

#### **SENSE Input**

The SENSE input provides a pin at which any system voltage can be monitored. If the voltage on this pin drops below  $V_{IT}$ , then  $\overrightarrow{RESET}$  is asserted. The comparator has a built-in hysteresis to ensure smooth  $\overrightarrow{RESET}$  sertions and de-assertions. It is good analog design practice to put a 1nF to 10nF bypass capacitor on the SENSE input to reduce sensitivity to transients and layout parasitics.

The AME8505 device can be used to monitor any voltage rail down to 0.405V using the circuit shown in Figure.1

Figure.1 Using AME8505 device to Monitor a User-Defined Threshold Voltage

#### Application Information (Contd.)

#### **Setting Reset Delay Time**

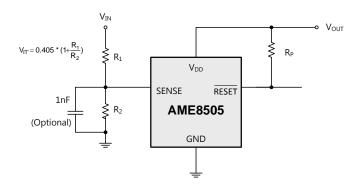

The AME8505 has three options for setting the RESET delay time as shown in Figure.2.

- Figure 2.1 shows the configuration for a fixed 300ms typical delay time by tying  $C_T$  to  $V_{DD}$ ; a resistor from 40k $\Omega$  to 200k $\Omega$  must be used. Supply current is not affected by the choice of resistor.

- Figure 2.2 shows a fixed 20ms delay time by leaving the  $C_T$  pin open.

- Figure 3.3 shows a ground referenced capacitor connected to C<sub>T</sub> for a user-defined program time between 1.25ms and 10s.

Figure.2 Configuration Used to Set the RESET Threshold Voltage

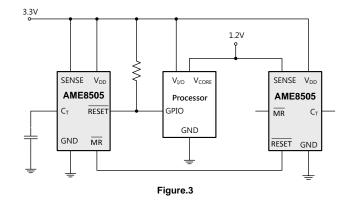

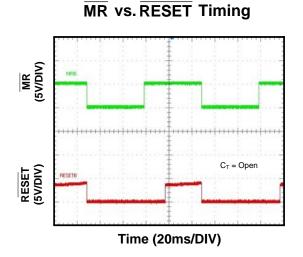

#### Manual Reset (MR) Input

$\overline{\text{MR}}$  input allows a processor or other logic circuits to initiate a reset. A logic low (0.3V<sub>DD</sub>) on  $\overline{\text{MR}}$  causes  $\overline{\text{RESET}}$  to assert. After  $\overline{\text{MR}}$  returns to a logic high and SENSE is above its reset threshold,  $\overline{\text{RESET}}$  is de-asserted after the user-defined reset delay expires. Note that  $\overline{\text{MR}}$  is internally tied to V<sub>DD</sub> using a 90k $\Omega$  resistor, so this pin can be left unconnected if  $\overline{\text{MR}}$  is not used.

See Figure.3 for how  $\overline{MR}$  can be used to monitor multiple system voltages (e.g. I/O supply voltage of some Processors should be setup before core voltage and processor can only start after both I/O and core voltages setup). Note that if the logic signal driving  $\overline{MR}$  does not go fully to V<sub>DD</sub>, there is some additional current draw into V<sub>DD</sub> as a result of the internal pull-up resistor on  $\overline{MR}$ .

#### Application Information (Contd.)

To minimize current draw, a logic-level FET can be used as illustrated in Figure.4.

Figure.4 Using an External MOSFET to Minimize  $I_{DD}$  When  $\overline{MR}$  Signal Does Not Go to  $V_{DD}$

#### **RESET** Output

The  $\overline{\text{RESET}}$  output is typically connected to the  $\overline{\text{RESET}}$  control pin of a microprocessor. For Open-Drain output versions, a pull-up resistor must be used to hold this line high when  $\overline{\text{RESET}}$  is not asserted. The  $\overline{\text{RESET}}$  output is active once  $V_{DD}$  is over  $V_{DD(min)}$ , this voltage is much lower than most microprocessors' functional voltage range.  $\overline{\text{RESET}}$  remains high as long as SENSE is above its threshold ( $V_{IT}$ ) and the  $\overline{\text{MR}}$  input is logic high. If either SENSE falls below  $V_{TT}$  or  $\overline{\text{MR}}$  is driven low,  $\overline{\text{RESET}}$  is asserted.

Once  $\overline{MR}$  is again logic high and SENSE is above (V<sub>IT</sub> +V<sub>HYS</sub>), the  $\overline{RESET}$  pin goes to a high impedance state after delay time (t<sub>D</sub>). The open-drain structure of  $\overline{RESET}$  is capable to allow the reset signal for the microprocessor to have a voltage higher than V<sub>DD</sub> (up to 5.5V). The pull-up resistor should be no smaller than 10 k $\Omega$  as a result of the finite impedance of the  $\overline{RESET}$  line.

#### Characterization Curve

#### 3.0 2.5 2.0 I<sub>DD</sub> (μΑ) 1.5 125°C 1.0 85°C 25°C -10ºC 0.5 -40°C 0.0 1 2 3 4 5 6 7 0 V<sub>DD</sub> (V)

#### Supply Current vs. Supply Voltage

### ■ Characterization Curve (Contd.)

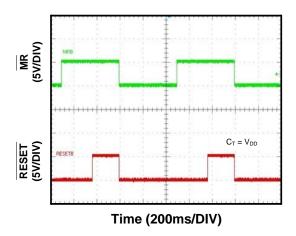

MR vs. RESET Timing

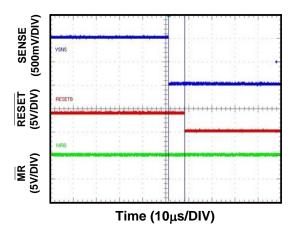

High to Low Level RESET Delay

SENSE vs. RESET Timing

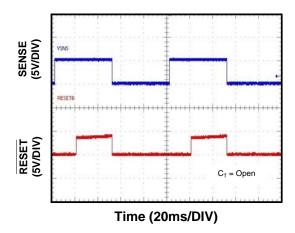

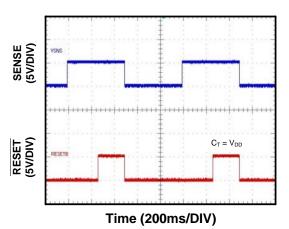

SENSE vs. RESET Timing

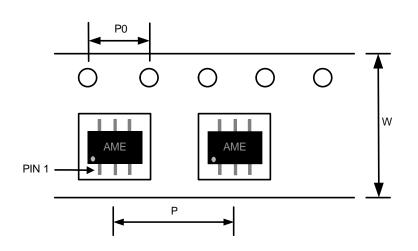

### ■ Tape and Reel Dimension

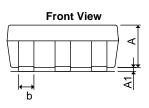

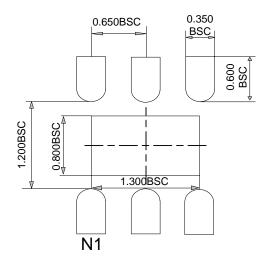

#### SOT-26

Carrier Tape, Number of Components Per Reel and Reel Size

| Package | Carrier Width (W) | Pitch (P)  | Pitch (P0) | Part Per Full Reel | Reel Size |

|---------|-------------------|------------|------------|--------------------|-----------|

| SOT-26  | 8.0±0.1 mm        | 4.0±0.1 mm | 4.0±0.1 mm | 3000pcs            | 180±1 mm  |

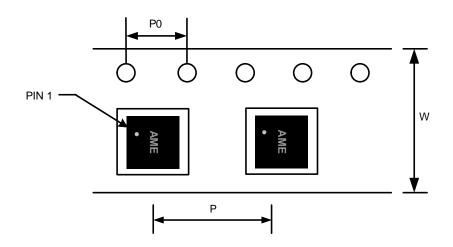

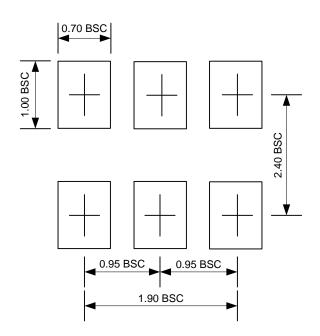

#### DFN-6D (2x2x0.75mm)

Carrier Tape, Number of Components Per Reel and Reel Size

| Package | Carrier Width (W) | Pitch (P)  | Pitch (P0) | Part Per Full Reel | Reel Size |

|---------|-------------------|------------|------------|--------------------|-----------|

| DFN-6D  | 8.0±0.1 mm        | 4.0±0.1 mm | 4.0±0.1 mm | 3000pcs            | 180±1 mm  |

#### Package Dimension

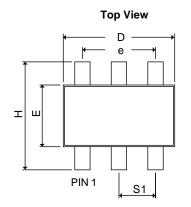

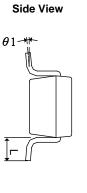

#### SOT-26

| SYMBOLS               | MILLI    | METERS          | INCHES         |                 |  |

|-----------------------|----------|-----------------|----------------|-----------------|--|

| STIVIDULS             | MIN      | MAX             | MIN            | MAX             |  |

| Α                     | 0.90     | 1.30            | 0.0354         | 0.0512          |  |

| <b>A</b> <sub>1</sub> | 0.00     | 0.15            | 0.0000         | 0.0059          |  |

| b                     | 0.30     | 0.55            | 0.0118         | 0.0217          |  |

| D                     | 2.70     | 3.10            | 0.1063         | 0.1220          |  |

| E                     | 1.40     | 1.80            | 0.0551         | 0.0709          |  |

| е                     | 1.90     | D BSC           | 0.0748 BSC     |                 |  |

| н                     | 2.60     | 3.00            | 0.1024         | 0.1181          |  |

| L                     | 0.37 BSC |                 | 0.014          | 6 BSC           |  |

| θ1                    | 0°       | 10 <sup>°</sup> | 0 <sup>°</sup> | 10 <sup>°</sup> |  |

| S₁                    | 0.9      | 5 BSC           | 0.0374         | 4 BSC           |  |

#### Lead Pattern

#### Note:

- Lead pattern unit description: BSC: Basic. Represents theoretical exact dimension or dimension target.

- 2. Dimensions in Millimeters.

- 3. General tolerance  $\pm 0.05$ mm unless otherwise specified.

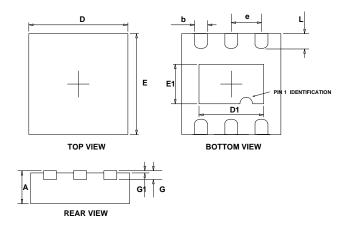

## Package Dimension (Contd.)

## DFN-6D

(2x2x0.75mm)

| SYMBOLS | MILLIM | ETERS | INC      | HES   |  |

|---------|--------|-------|----------|-------|--|

| STWBULS | MIN    | MAX   | MIN      | MAX   |  |

| Α       | 0.700  | 0.800 | 0.028    | 0.031 |  |

| D       | 1.900  | 2.100 | 0.075    | 0.083 |  |

| E       | 1.900  | 2.100 | 0.075    | 0.083 |  |

| е       | 0.650  | )TYP  | 0.026TYP |       |  |

| D1      | 1.100  | 1.650 | 0.043    | 0.065 |  |

| E1      | 0.600  | 1.050 | 0.024    | 0.041 |  |

| b       | 0.180  | 0.350 | 0.007    | 0.014 |  |

| L       | 0.200  | 0.450 | 0.008    | 0.018 |  |

| G       | 0.178  | 0.228 | 0.007    | 0.009 |  |

| G1      | 0.000  | 0.050 | 0.000    | 0.002 |  |

## Lead Pattern

#### Note:

1. Lead pattern unit description:

BSC: Basic. Represents theoretical exact dimension or dimension target.

- 2. Dimensions in Millimeters.

- 3. General tolerance  $\pm 0.05$ mm unless otherwise specified.

#### www.ame.com.tw E-mail: sales@ame.com.tw

Life Support Policy:

These products of AME, Inc. are not authorized for use as critical components in life-support devices or systems, without the express written approval of the president

of AME, Inc.

AME, Inc. reserves the right to make changes in the circuitry and specifications of its devices and advises its customers to obtain the latest version of relevant information.

© AME, Inc. , January 2024

Document: G004A-DS8505-C.01

# Corporate Headquarter AME, Inc.

8F-1, 12, WenHu St., Nei-Hu Dist., Taipei 114, Taiwan.. Tel: 886 2 2627-8687 Fax: 886 2 2659-2989